System Verilog for Verification

April 6, 2023 2023-04-11 8:25System Verilog for Verification

System Verilog for Verification

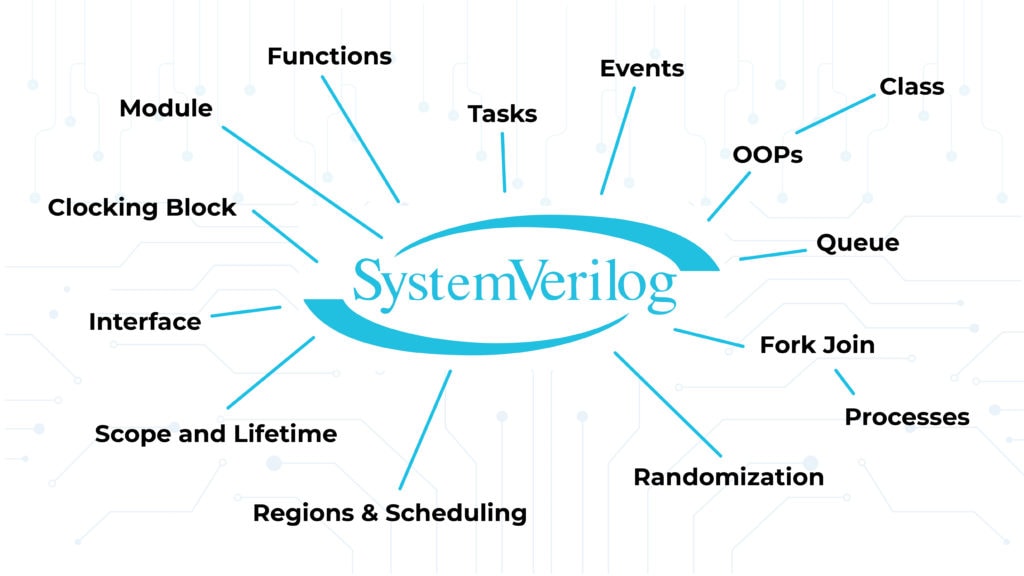

A comprehensive online course that covers all the constructs in System verilog. Description of each construct along with examples and coding assignments enable thorough learning

Duration: 13 weeks

Price Starting from: ₹ 1000

Course Syllabus

Basic Building Blocks, Module, Program Block, Function, Task, Class, Display Format Specifications & System Routines

Data Types 1, Data Types 2, Literal, String, String Methods, Fixed Array, Packed Array, Unpacked Array, Dynamic Array, Dynamic Array Methods, Associative Array, Associative Array Methods, Queue, Queue Methods, Array Manipulation Methods, User Defined Datatype, Enumeration, Enumeration Methods, Structure, Union, Event, Event Methods, Scope & Life Time – How long a variable is active

Operator & Streaming Operator

Sub-Routines, Blocking, Non-Blocking, Event Region & Scheduling, Selection Statement, Loop Statement, Jump Statement & Named Block

Processes, Fork Join, Fine-Grain Process & Final Block

Connecting Testbench and DUT, Interface, Clocking Block, Virtual Interface & Package

Class, Handle, Shallow & Deep Copy, Static Variable & Method, this keyword, Inheritance & Polymorphism

Randomization & Randomization Methods

Mailbox, Mailbox Methods, Semaphore & Semaphore Methods

Functional Coverage & Direct Programming Interface

Prerequisites

- Basic programming knowledge

- Awareness of SystemVerilog

- Basic knowledge about ASICs

What will I learn

- Basic programming in System Verilog

- Object Oriented Programming Concepts

- How to use Simulator to compile and run System Verilog programs