Inheritance in System Verilog

April 5, 2023 2023-05-02 13:25Inheritance in System Verilog

System Verilog (SV) language has object-oriented constructs primarily used in verification. Verification programs in SV use object-oriented structures called classes to achieve their functionality. The relationships between classes are utilized in the execution of the object-oriented program.

Relationships define how the instances of the classes, (i.e.) objects of the classes, interact with each other. Primarily, two types of relationships exist between classes, namely, “has-a” and “is-a”. The “has-a” relationship is also known as a containment relationship. In the relationship, the instance of a class contains an (or “has an”) instance of another class. The “is a” relationship is also known as an inheritance relationship.

Inheritance brings together a set of related classes. These classes are of similar type, meaning, the classes have common functionality.

For example, during the verification process, a set of test cases are executed. Each test case generates test-specific stimuli that are eventually provided to the design under test. Besides the data or signals generated, the remaining functionality of all the test cases remains the same. So, each test is a type of test case. Hence, we can create an inheritance structure, with all the functionalities being within a base class or a parent class called a test case. Each test case inherits from the parent class and is referred to as the child class.

By inheriting we mean, that all the methods and variables (that is, functionality and characteristics) of the parent class are also available in the child classes. In SV, the child class uses the keyword extends to inherit from the parent class. Inheritance also enables a functionality called polymorphism by which child classes can alter the functionality of a parent class’ method. Based on the class that is instantiated the appropriate method is invoked at runtime.

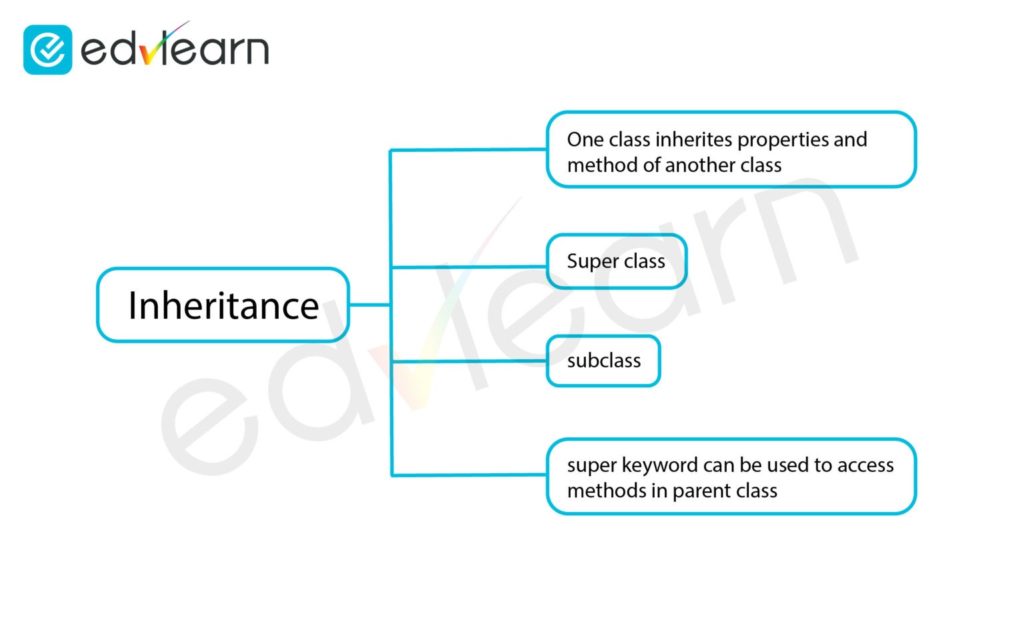

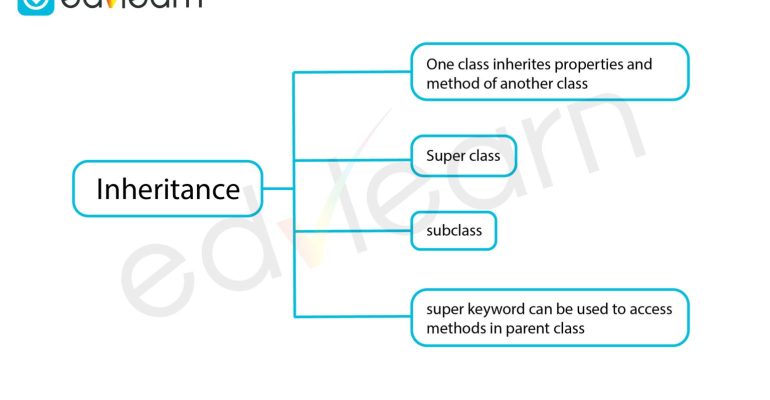

Given here is a mind-map that captures various aspects of inheritance. Check out our comprehensive course on System Verilog for Verification for more details and examples of all System Verilog Verification constructs.