Monitors – The eyes of a TestBench!

April 5, 2023 2023-05-02 13:25Monitors – The eyes of a TestBench!

In the chip development process, the functionality of a chip is captured in RTL code typically written in a Hardware descriptive language. RTL code is functionally verified. monitor

Functional verification of a chip is done by writing a test bench. A testbench is a software that is built around a chip to provide stimulus and check the correctness of the chip. Typically test benches are layered and have components that have well-defined roles. In this article, we will go over the test bench component monitor.

The majority of the chips developed today are System On Chip or SOC. SOC would have multiple sub-systems and while developing, each sub-system would be designed by multiple designers wherein each would own a part of the sub-system. Verification would be done at unit level and then at sub-system level and then at SOC level.

A typical design unit that is taken up for verification also called Design under test or DUT, would have multiple interfaces through which the unit would get inputs and send outputs.

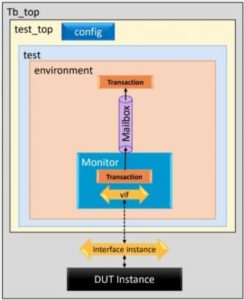

Monitor is a component in the test bench that observes a bus interface. Monitor observes the interface, based on the protocol in the interface, captures and converts the signals in the interface into a transaction. It broadcasts the observed transaction for the rest of the test bench to analyze and check. Each interface would need to have an associated monitor.

In a test bench, monitors are passive components – that is, they do not drive any pin. They are like the eyes of the test bench and hence need to constantly look at all the signals that they are monitoring every cycle. They should be designed as plug-and-play.

While designing monitors, one needs to determine what persistence it would keep, what variables it would broadcast, what checkers it would have, and how often it would broadcast.

Diagram 1: Monitor, monitors signals through virtual interface, converts to transaction and broadcasts

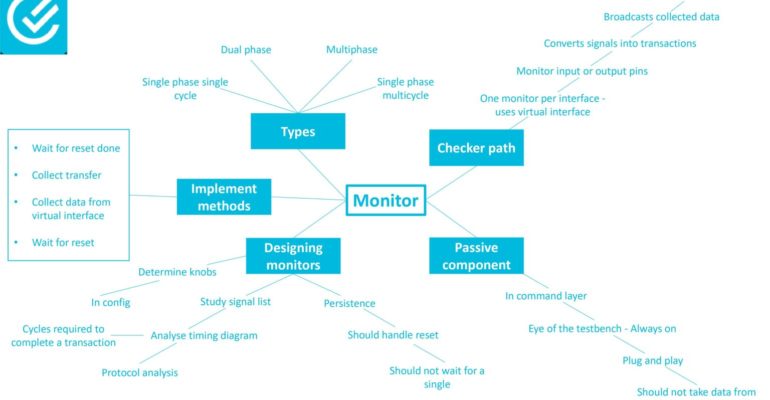

Shown here is a mind map that captures various aspects of a monitor:

Diagram 2: Mind-map that captures various aspects of monitor

There are protocols for which monitors can be simple and there are protocols for which monitors could get complex.

Check out our comprehensive course on writing a System Verilog test bench for more details and examples of all test bench components.